Field-Programmable Gate Array (FPGA)

Field-programmable gate array (FPGA) adalah perangkat semikonduktor yang dapat diprogram, berisikan blok-blok logika yang dapat dikonfigurasi atau configurable logic blocks (CLBs) dalam bentuk matriks yang saling terhubung (xilinx, n.d.). FPGA juga dapat digunakan untuk membuat sirkuit yang suatu yang dapat dioptimalkan seperti pemrosesan sinyal digital / Digital Signal Processing (DSP), pembelajaran mesin, dan sebagainya. Saat ini FPGA dapat ditemukan di beberapa peralatan elektronik serta peralatan khusus, seperti satelit dan peralatan komunikasi. (Hymel, 2021)

Icestick Lattice FPGA

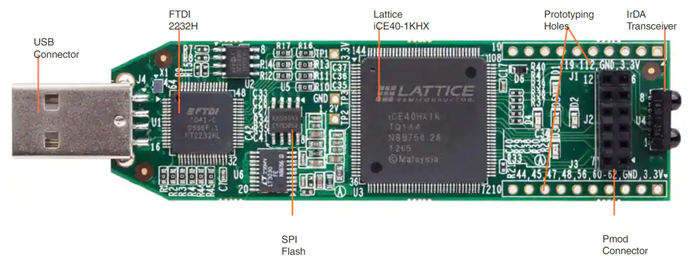

Dalam tutorial ini digunakan board FPGA jenis Icestick Evaluation Board dengan kode produk ICE40HX1K-STICK-EVN yang berukuran cukup kecil dan berbiaya rendah dari Lattice Semiconductor yang menggunakan FPGA keluarga ICE40,

Gambar 1. ICEstick Evaluation Board (iCEstick Evaluation Kit – User’s Guide, 2014)

Beberapa fitur ataupun komponen yang ada dalam Icestick Evaluation Board antara lain:

- iCE40HX1K FPGA

- FTDI 2232H USB yang dapat digunakan untuk pemrograman dan antarmuka UART ke PC

- Vishay TFDU4101 IrDA transceiver

- Lima buah LED

- 2 x 6 konektor kompatibel Diligent PmodTM untuk beberapa jenis koneksi periferal

- Discera 12Mhz MEMS oscillator

- SPI Flash Micron 32Mbit N25Q32,

- Dukungan dari Lattice iCEcube2™ design software,

- Konektor USB yang menyediakan suplai daya,

- 16 koneksi I/O digital LVCMOS/LVTTL (3.3V)

Secara umum, pembuatan desain FPGA melalui beberapa tahapan, dimulai dari penulisan program atau kode HDL, simulasi, synthesis, Place and Routing (PNR), pemaketan, hingga proses upload ke IC FPGA (Hymel, 2021).

Penulisan kode HDL, Terdapat tiga bahasa deskripsi perangkat keras yang paling popular, yaitu VHDL, Verilog, dan SystemVerilog. Pada tulisan ini akan digunakan Bahasa Verilog, keran Bahasa ini adalah yang didukung oleh tools yang akan digunakan dalam tulisan ini.

Simulasi – simulasi digunakan untuk memastikan semua desain berfungsi, sebelum membuat dan mengunggah desain tersebut ke FPGA. Untuk melakukan simulasi, dibituhkan kode tes “testbench” dengan menambahan kode HDL berupa input dan sinyal clock untuk mengamati perilaku output dalam program simulasi. Pada tulisan ini testbenches ditulis dalam kode Verilog dan desain disimulasikan melalui gtkwave.

Sintesis – Karena HDL bukan bahasa prosedural (yaitu kode Anda tidak dijalankan secara berurutan dalam prosesor), HDL tidak dapat “dikompilasi”. Sebaliknya, proses “sintesis” merupakan proses pengubahan kode HDL menjadi representasi gerbang logika yang dapat dipahami oleh FPGA. Intinya, itu mengubah kode menjadi sirkuit digital. Pada tutorial ini digunakan software yosys untuk melakukan sintesis.

Place and Route (PNR) – PNR berfungsi untuk menghubungkan berbagai bagian di dalam FPGA yang digunakan/ditentukan sesuai desain yang dirancang dalam HDL. Prosesnya mirip dengan menggunakan autorouter dalam program desain PCB. Pada tutorial ini PNR yang diguanakan adalah nextpnr.

Package – dibutuhkan software pemaketan untuk mengubah kode ascii ke kode biner agar dapat dibaca oleh proses konfigurasi FPGA. Dalam proses ini digunakan tools icepack yang merupakan bagian dari proyek ICEStorm.

Upload – langkah terakhir adalah mengupload file biner ke FPGA.

APIO

Apio (diucapkan [ˈa.pjo]) merupakan toolbox multiplatform, yang terdiri dari dari paket pre-built statis, tools untuk melakukan konfigurasi, dan antarmuka perintah untuk memverifikasi, mensintesis, mensimulasikan, dan meng-upload desain Verilog (Torrens & González, 2022). Sehingga semua tools yang dibutuhkan untuk mendesain FPGA seperti di atas, dari simulasi, sintesis hingga upload ke FPGA tidak perlu diinstall satu-persatu.

Gambar 2. Diagram Alir Penggunaan FPGA (Hymel, 2021)

Install Apio pada Windows

Apio merupakan tools berbasis Python untuk mengatur tools tingkat rendah lainnya, dari mulai driver, yosys, icepack, iceprog dan yang lainnya . Apio tidak hanya digunakan untuk papan Icestick Evaluation Board, tapi juga beberapa papan FPGA lainnya. Daftar pepapan yang didukung oleh apio dapat dilihat pada laman https://github.com/FPGAwars/apio#supported-boards .

Untuk dapat menginstall Apio, pastikan PC yang digunakan sudah terinstall Python 3 dan pip.

Buka commad promt, lalu Instal apio versi terakhir dengan perintah

> pip install -U apio

Setelah apio terinstall, jalankan command prompt kembali sebagai administrator

Dari command prompt, jalankan perintah berikut untuk menginstall driver, contoh progam dan semua tools yang disediakan

> apio install -all

Perintah di atas juga akan meng-install driver FTDI yang dibutuhkan untuk berkomunikasi dengan papan ICEStick melalui port USB

Jalankan perintah apio drivers –ftdi-enable untuk membuka tools Zadig, lalu pilih menu “Opton > List All Devices”

Pada pilihan board di menu drop-down, pilih “Lattice FTUSB Interface Cable (Interface 0)”, jika tidak ada pilih “Dual RS232-HS (interface 0)”, lalu pilih driver libUSBK dan klik “Replace Driver”

Perhatian:

Khusus yang terdeteksi board “Dual RS232-HS (interface 0)”, pada file boards.js ganti pada bagian icestick.ftdi.desc menjadi “Dual RS232-HS” agar tidak terjadi error saat upload.

Apio menyediakan contoh-contoh program untuk beberapa board yang didukungnya. Untuk melihat daftar semua contoh program dapat menggunakan perintah

> apio examples -l

untuk menyalin contoh program gunakan opsi -d seperti berikut

> apio examples -d icestick/leds

Perintah di atas akan menyalin program led ke dirtektori icestick\leds dari direktori aktif, masuk ke direktori leds dengan perintah cd icestick\leds. Dalam direktori leds terdapat beberapa file, diantaranya apio.ini yang beriei jenis board yang digunakan, leds.pcf yang mendefinisikan pin input/output, leds.v adalah file Verilog yang berisi kode program HDL, leds_tb.v adalah file testbench untuk melakukan menggunakan Bahasa Verilog. File apio.ini dapat di-generate menggunakan perintah

> apio init -b icestick

Setelah masuk ke dalam direktori leds, lalu verifikasikan kode Verilog dengan perintah untuk memastikan tidak ada kesalahan kode.

> apio verify

jika kode Verilog sudah diverifikasi, kita bisa menjalankan simulasi desain FPGA mengunakan perintah

> apio sim

perintah di atas akan menjalankan aplikasi gtkwave seperti pada gambar di bawah. Pada gambar tersebut ditunjukan bahwa kelima led (D1 hingga D5) semuanya dalam kondisi HIGH.

Setelah simulasi dianggap sudah sesuai, kode Verilog dapat disintesis dan routing dengan satu perintah, yaitu

> apio build

Hasil dari sintesis dan place and routing tersebut dapat diupload ke FPGA dengan perintah

> apio upload

Setelah proses upload sukses, dapat dilihat di board FPGA icestick kelima led yang ada di papan tersebut menyala semua.

Daftar Pustaka

Hymel, S. (2021, 11 08). Introduction to FPGA Part 1 – What is an FPGA? Retrieved 11 15, 2022, from Digi-Key Electronics: https://www.digikey.com/en/maker/projects/introduction-to-fpga-part-1-what-is-an-fpga/3ee5f6c8fa594161a655a9f960060893

iCEstick Evaluation Kit – User’s Guide. (2014). Retrieved 11 1, 2022, from Lattice Semiconductor: https://www.latticesemi.com/view_document?document_id=50701

Torrens, J. A., & González, J. (2022, 11 5). Apio: Open source ecosystem for open FPGA boards. Retrieved 11 20, 2022, from Github: https://github.com/FPGAwars/apio

xilinx. (n.d.). What is an FPGA? Retrieved from Xilinx.com: https://www.xilinx.com/products/silicon-devices/fpga/what-is-an-fpga.html